2024年5月29日,bv伟德源自英国始于1946微纳器件研究团队詹学鹏教授、陈杰智教授参与由山西大学韩拯教授、辽宁材料实验室王汉文副研究员团队主导的研究,在Nature杂志在线发表题为“Van der Waals polarity-engineered 3D integration of 2D complementary logic”的研究论文。伟德BETVLCTOR1946詹学鹏教授为论文共同第一作者,伟德BETVLCTOR1946为共同第一作者单位。

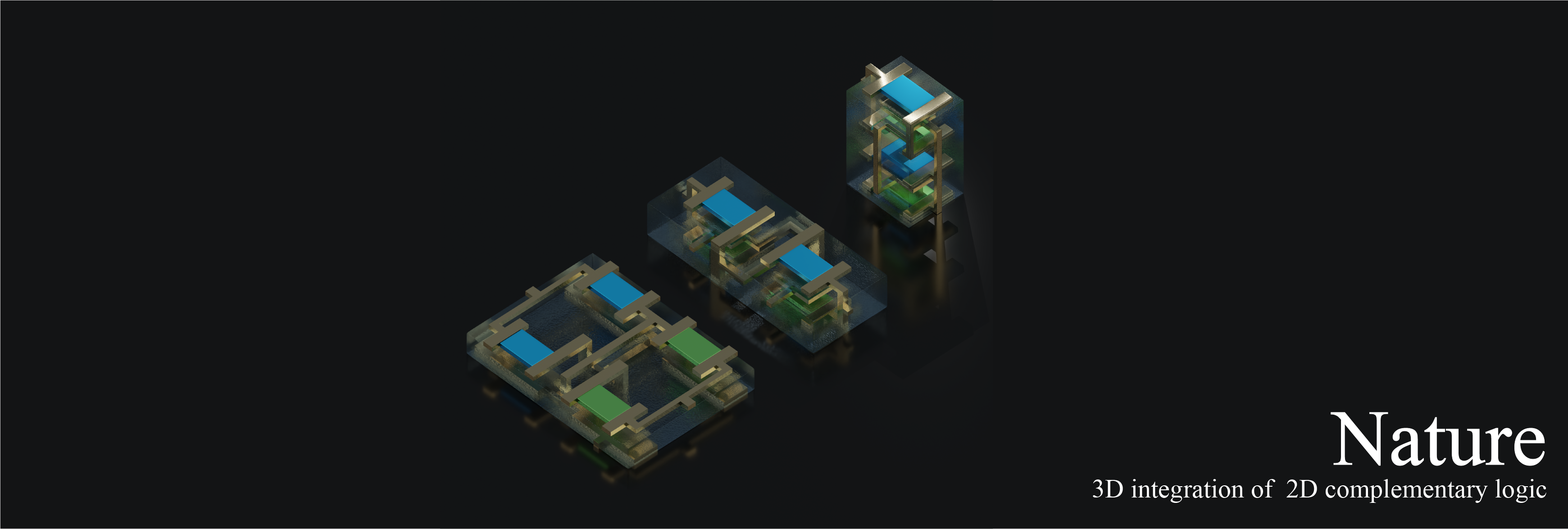

集成电路芯片特征尺寸微缩已逐渐趋近物理极限,二维半导体材料单片三维集成是维系高性能集成电路芯片发展的重要途径。受限于二维材料掺杂工艺,器件通常表现为电子输运主导,因此,如何实现高性能空穴输运晶体管器件,并构建单片三维集成芯片成为重要科技挑战。面向新型二维材料在三维垂直集成设计中的关键问题,信息学院微纳器件研究团队与山西大学、辽宁材料实验室、中山大学、中国科学院大学、北京大学、上海科技大学、中国科学院金属研究所等多单位联合攻关,提出了一种基于界面耦合效应掺杂策略,通过反铁磁绝缘材料氯氧化铬(CrOCl)薄膜调控二硫化钼(MoS2)的费米能级,在不破坏沟道情况下实现载流子极性调控,器件空穴迁移率高达425cm2V-1s-1、开关比超106、在空气中保存1年以上性能没有明显退化。该工艺方案具有简单、稳定、清洁等优势,进一步通过垂直堆垛设计,最高实现由14层范德华材料构成的3D NAND和3D SRAM等垂直集成互补逻辑器件电路。研究成果突破了二维平面晶体管集成的维度限制,有望为推动后摩尔时代高性能集成电路芯片发展提供重要科学参考。

原文链接

https://www.nature.com/articles/s41586-024-07438-5